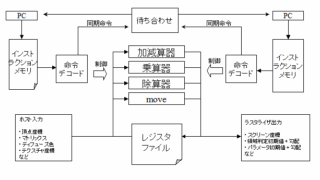

FPGA

FPGA 作成した浮動小数点演算ライブラリの整理

作成した浮動小数点演算ライブラリを整理してみました。XILINXのIP使えば済む話ではあるのですが、 ・低精度でいいけど高速な逆数計算が欲しかった(本命) ・非正規化数とか例外とか不要なのでコンパクトにしたい ・IPコア使うと verita...

FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA