FPGA

FPGA Zybo 開発環境構築記

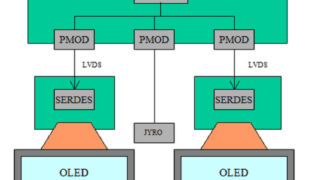

長らくZyboを眠らせたままでしたが、ちょっとだけ余裕が出てきたのでRealTime-GPUの設計を再開いたしました次第ですが、MIPI CSI-2 に挑戦したくて、Zybo Z7 を購入し、折角なのでちゃんと Zybo を Zybo らし...

FPGA

FPGA  技術記事

技術記事  技術記事

技術記事  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  計算機科学

計算機科学  FPGA

FPGA  技術記事

技術記事