LUT-Network

LUT-Network LUT-Networkの最新資料更新

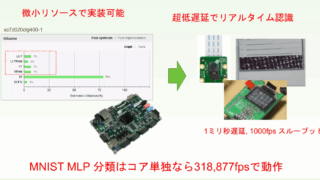

FPGAXでお話のお時間を頂いて資料を作ってからある程度開発が進展してきました。Twitter上中心に、多くの方からご支援いただけたことをまことに感謝しております。特に marsee101さんには、FPGAの部屋にてBinaryBrainの...

LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network