技術記事

技術記事 カメラの種類(カラー/モノクロ、ローリング/グローバル)

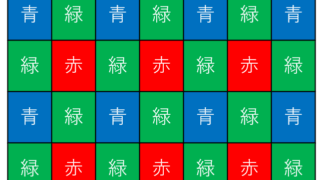

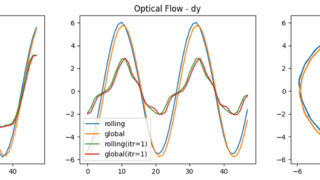

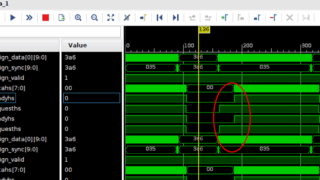

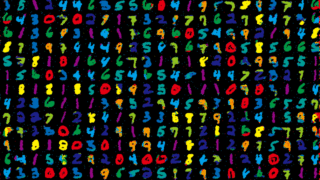

はじめにタイトル長くなったのでカメラとしましたが、正確に言うと半導体イメージセンサーの話です。本当にいろんな種類があるのですが、メジャーなものとして非常にざっくりと、BAYER配列のカラーイメージセンサとモノクロイメージセンサの話と、ローリ...

技術記事

技術記事  技術記事

技術記事  技術記事

技術記事  技術記事

技術記事  技術記事

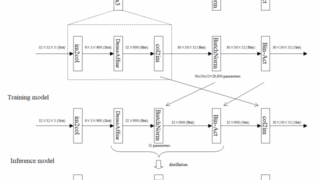

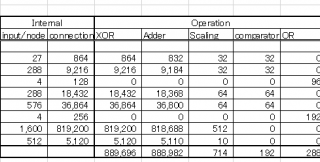

技術記事  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

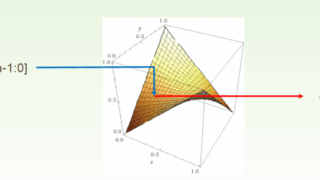

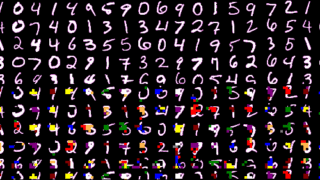

LUT-Network  Deep Learning

Deep Learning