計算機科学

計算機科学 視覚のハッキングについての考察

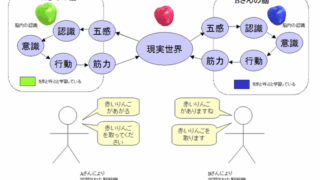

以前書いたように、作成中のリアルタイムGPUを用いた電脳メガネの作成を企て中です。そこで電脳メガネの究極の目的は視覚のハッキングと以前書きましたが、視覚のハッキングとは何か、ということをもう少し考察しておこうと思います。考察に先立って、人が...

計算機科学

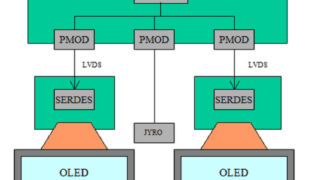

計算機科学  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  計算機科学

計算機科学  FPGA

FPGA  計算機科学

計算機科学  技術記事

技術記事  FPGA

FPGA  FPGA

FPGA