FPGA

FPGA 組み込み屋の為のVerilog入門 その5 VALID&READYのハンドシェーク

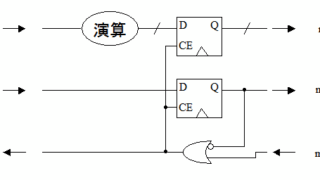

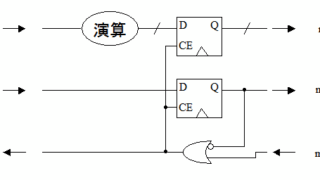

<はじめに> 最近はXILINXが各コアでAXIバス(ARM社AMBAバス仕様の1つ)を使い始めていることもあって、VALIDとREADYでのハンドシェークを用いることが増えてきた。 この方式に限った話ではないのだが、バスプロトコル関係のハ...

FPGA

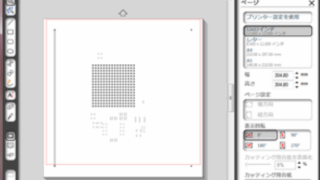

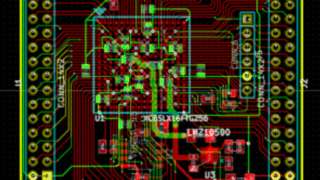

FPGA  基板作成

基板作成  基板作成

基板作成  体験記

体験記  基板作成

基板作成  FPGA

FPGA  技術記事

技術記事  FPGA

FPGA  計算機科学

計算機科学  FPGA

FPGA