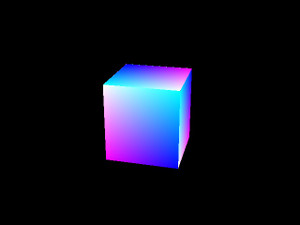

とりあえずRTLに起こしてみて、ラスタライザまでシミュレーションできたので上げておきます。

ラスタライザ出力段階で既にそれなりの絵になってますね。実際はこれを逆数とって(パースペクティブ補正)UVアドレスにして、以前作成したテクスチャキャッシュと繋げて、テクスチャマッピングまでやりたいです。

ラスタライズコアのZybo(XC7Z010-1CLG400)向けのISE14.7での合成結果は

Number of Slice Registers 4765(13%)

Number of Slice LUTs 3524(20%)

Minimum period: 2.442ns (Maximum Frequency: 409.500MHz)

[普段 Vivado ですが、合成段階でさくっと周波数出してくれるISEはこんなとき便利です]

となります。

DSPやBRAMは未使用で、LUT(Distributed-RAM)にシャドウレジスタバンクつきのバーテックスバッファを構成し、各種演算もすべてインクリメント演算(加算器)だけで実現しています。なので上記が全使用リソースになります。

Zソートは基本は書いていますが、まだ入れていなくて、カリングのみで陰面消去しています。

とりあえず収まらないと始まらないと思い、立方体1個のみ描けるように、エッジ判定12本、ポリゴン数6でセッティングしています。

ただ実際合成してみるとまだ回路容量あるので、案外いろいろ入りそうな予感がします。

(最新のUltraScale+ とか使えるなら実質無尽蔵に入るんじゃなかろうかとさえも思えますね)

当方、基本的にリアルタイムシステムやりつつ、普段は主にCV(Computer Vision)扱うお仕事なのですが、趣味のCG(Computer Graphics)でどこまでやれるか楽しみです。

先に試した9軸ジャイロセンサはZynqのPS(ARMコア)のみで制御可能で、PLのロジック消費に影響ないので組み合わせで追加コストは無いはずです。最終目標として、CGをリアルタイムにジャイロに同期させてグリグリ動かすことを目標にしています。

原理上、頂点座標確定と同時に遅延ゼロでHDMI出力を開始できるアーキテクチャですので、VR/AR向けなリアルタイム描画が出来ればと思う次第です。

(同日追記)

ややむりやり実機に突っ込んでみました。あー、ポリゴン未存在部分の初期化書き間違えた。でも動いてる!

もろもろシミュレーションで再現したので修正して再合成中…

今回はuv座標ではなくRGBを普通にグーローシェーディングしてる。

RGBの配色を間違えた気がするが、それ以外は、無事シミュレーションと一致(のはず)

HDMIとVGAの同時出力も問題なし

めでたしめでたし

回路規模は周辺も全部いれて意外とおとなしいサイズに入りました。

とりあえず今週はここまで。

コメント