拙作のJellyでも非同期FIFOを用意しているが、こちら などを参考にさせていただくと、FPGAでの非同期の扱いは奥深いことがわかる。

そこで、XILINXの coregen で生成した非同期FIFOのネットリストを解析してみた。

ターゲットは XC6VLX75T-2FF484 として、DistributedRAMで幅1bit深さ16での生成。

ざっとネット名から推論する限りライトポインタとリードポインタをそれぞれグレイコード化してやり取りしている一般的なFIFOに見受けられる。

まず、netgenでverilog化

【wr_clk側 4bitグレイコードの0bit目】

FDC #(

.INIT ( 1'b0 ))

\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_pntr_gc_0 (

.C(wr_clk),

.CLR(wr_rst),

.D(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/WR_PNTR[0]_WR_PNTR[1]_XOR_3_o ),

.Q(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<0> [0])

);【rd_clk側 ダブルFF 1段目】

FDC #(

.INIT ( 1'b0 ))

\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_pntr_gc_0 (

.C(wr_clk),

.CLR(wr_rst),

.D(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/WR_PNTR[0]_WR_PNTR[1]_XOR_3_o ),

.Q(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<0> [0])

);

FDC #(

.INIT ( 1'b0 ))

\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/gsync_stage[1].rd_stg_inst/Q_0 (

.C(rd_clk),

.CLR(rd_rst),

.D(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<0> [0]),

.Q(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<1> [0])【rd_clk側 ダブルFF 2段目】

FDC #(

.INIT ( 1'b0 ))

\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/gsync_stage[2].rd_stg_inst/Q_0 (

.C(rd_clk),

.CLR(rd_rst),

.D(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<1> [0]),

.Q(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<2> [0])

);【rd_clk側 ダブルFF後論理へ (トリプルFFではない)】

LUT4 #(

.INIT ( 16'h6996 ))

\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_pntr_gc_asreg_last[3]_reduce_xor_81_xo<0>1 (

.I0(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<2> [0]),

.I1(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<2> [1]),

.I2(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<2> [2]),

.I3(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_q<2> [3]),

.O(\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gcx.clkx/wr_pntr_gc_asreg_last[3]_reduce_xor_8_o )

);

pcfファイルなどを見る限りに

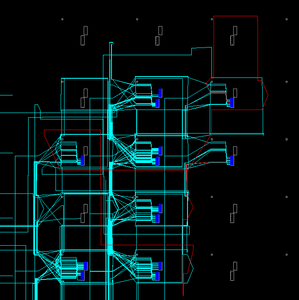

でもって、FPGAエディタで覗く。

ダブルFFは隣に並んでいるが、ルーティングが見た目に遠いような。メタステーブル対策これでいいのか???

ちなみに500MHz overの制約で合成してみたんだがタイミングMETしている模様。

コメント