LUT-Network

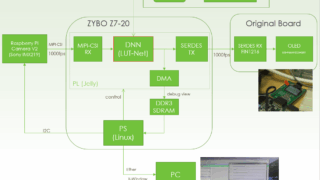

LUT-Network LUT-Networkの実機への組み込み

ひとまず実際にFPGAに組み込んで動き始めたので一旦ブログにも記載しておきます。 なおLUT-Network学習用の環境(BinaryBrain)はgithubにて公開しながら日々開発中です。以前やったRaspberry PI用カメラ(Ra...

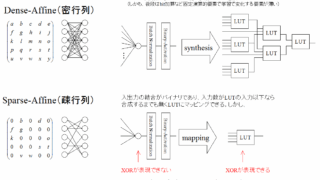

LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  LUT-Network

LUT-Network  FPGA

FPGA