久しぶりに以前の続きです。

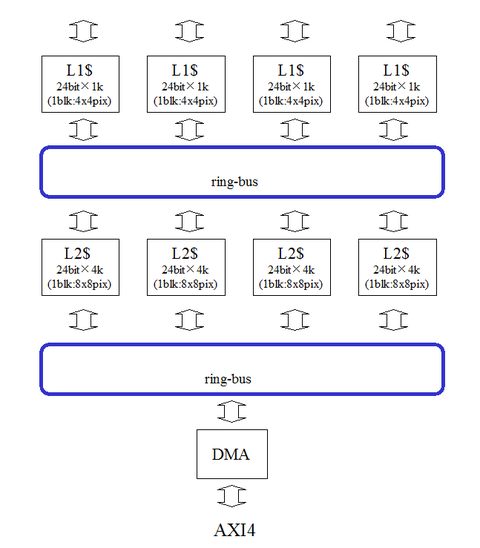

下記のようなアーキテクチャでGPU用のテクスチャキャッシュを試作してみました。

この上にバイリニア補間を行うSamplerが乗っかればそれっぽくなるはずです。

軽量なリングバスを実験的に入れてみましたので各ユニットのサイズや個数は可変です。

バイリニア補間に4点使うので、4回アクセスを4並列でやればパフォーマンス上バランスがいいかなって事で、4並列で設定して合成して見ました。シミュレーションではまあまあ目論みどおりの挙動で動いているようです。

この構成だとテクスチャキャッシュだけで ZC7Z010CGL400 のBRAMを50%消費してしまいました(LUTは15%程度、周波数はISE合成で389MHzでした)。

ちなみにデータは書き込みの際に8×8ピクセルのブロック単位で、それぞれ保存するようにし、アクセス方向に対するパフォーマンス変動を抑えられるようにして見ました。

また RGB 24bit だとアクセス効率が悪そうなのでRGBも分解して個別に置くようにしています。

L1キャッシュは上に載る予定のSamplerユニット毎に1対1で対応、L2キャッシュはメモリのアドレスに対して1対1で対応するようにしつつ、以前考察したナンプレ式の対応表としています。

この方式もシミュレーションを見る限りはそこそこうまくいっているようです。

今日はここまでです。まともに動くのはいつになるやら…

コメント